PROJETOS DE AUTOMAÇÃO INDUSTRIAL

Desde sua criação, os Controladores Lógicos Programáveis têm sido aplicados com sucesso em praticamente todos os segmentos da indústria, incluindo siderúrgicas, fábricas de papel, indústria química e usinas de energia. Os CLPs realizam uma grande variedade de controle, do simples controle repetitivo (ON-OFF) de máquinas simples até a fabricação sofisticada de controle de processos. Analise as assertivas a seguir:

I - O uso de CLPs pode substituir os painéis de relés em praticamente todas as aplicações.

II - Se os requisitos do sistema exigirem flexibilidade ou crescimento futuro, o CLP traz retornos que superam qualquer vantagem de custo inicial de um controlador de relés.

III - Pode-se fornecer energia a um motor elétrico trifásico de até 25 kW através de um contator acionado por uma saída digital do módulo do CLP, permitindo o controle do seu acionamento.

IV - Mesmo em aplicações extremamente simples, utiliza-se o CLP para reduzir os custos, quando comparados com o custo do uso de painéis de relés.

Assinale a alternativa CORRETA:

Apenas as sentenças I e II são verdadeiras.

Todas as sentenças são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas a sentença IV é falsa.

Apenas a sentença I é falsa.

O circuito eletrônico usado é padrão para a maioria das malhas de controle, independente da variável sendo medida ou manipulada.

Acerca do controlador de ação direta, verifique as assertivas seguir:

I) Um controlador de ação direta é um controlador de malha fechada, cuja saída variável de controle aumenta em resposta a um aumento na variável de processo.

II) Um exemplo de aplicação de controlador de ação direta é um sistema de resfriamento de ar.

III) Um controlador de ação direta é um controlador de malha fechada, cuja saída variável de controle diminui em resposta a um aumento na variável de processo.

Está(ão) correta(s):

I e II.

Apenas a III.

II e III.

Apenas a II.

Apenas a I.

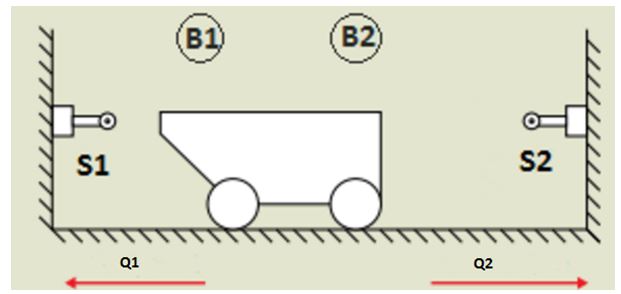

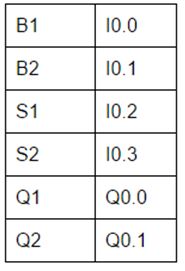

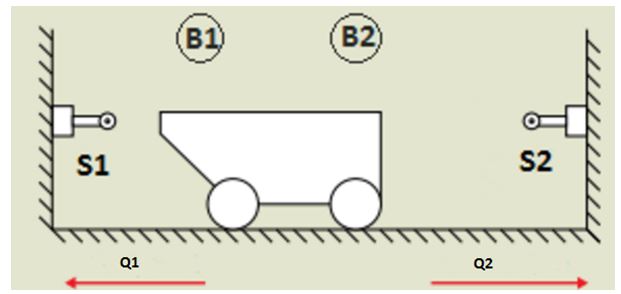

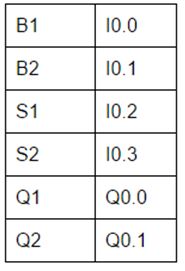

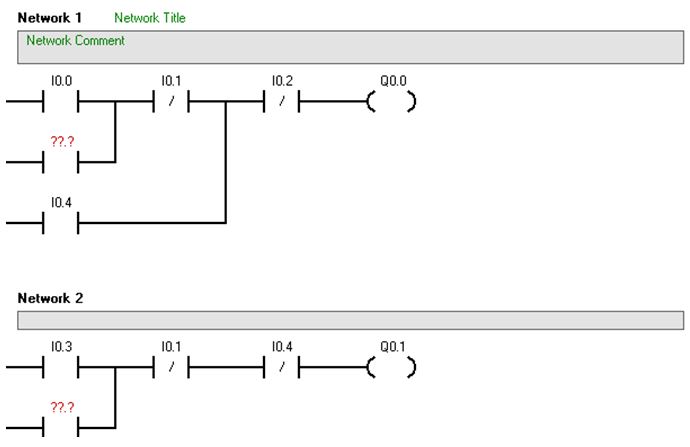

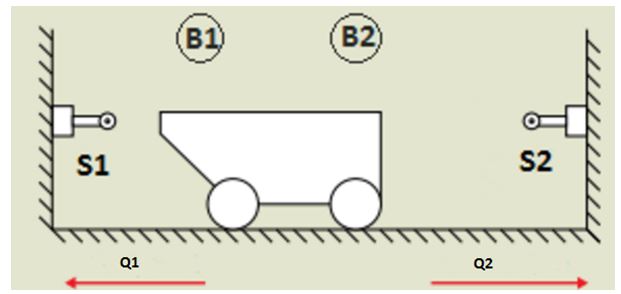

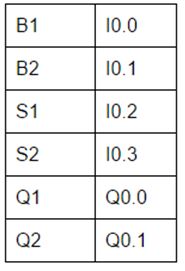

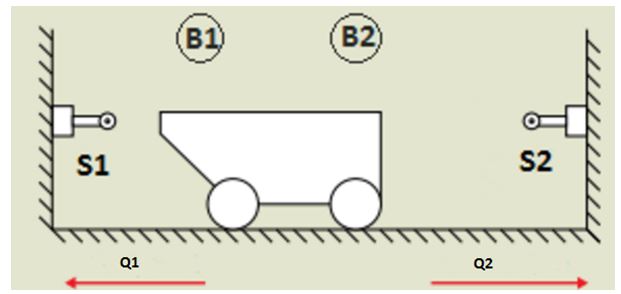

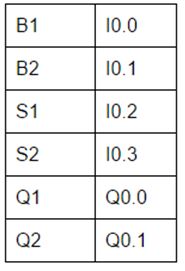

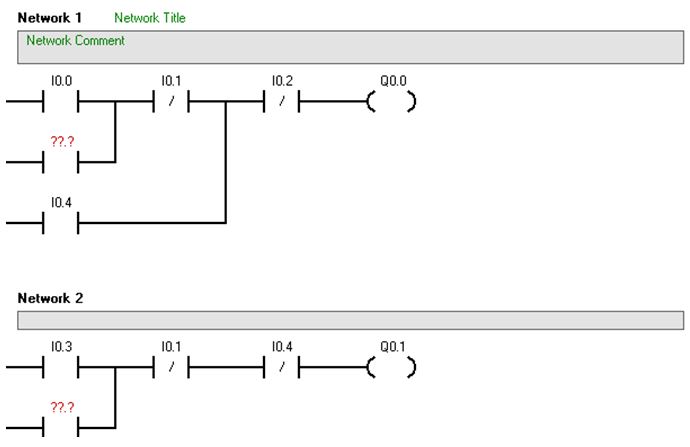

Verifique um programa do CLP para automatizar um carro transportador que deve funcionar da seguinte maneira: o operador pressiona um botão B1 para dar o comando, ligará o motor na direção preferencial do sensor S1. Uma vez o sensor de fim de curso S1 acionado, irá no movimento inverso, chegando em outro sensor fim de curso S2. A figura a seguir representa como deve ser o processo. Por fim, há um botão de parada B2.

Porém o programa está incompleto, bastando apenas nomear as funções:

Verifique as alternativas a seguir e veja qual completa corretamente o programa:

Network 1 → I0.0 e Network 2→ I0.1.

Network 1 → Q0.1 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.0.

Network 1 → I0.1 e Network 2→ I0.2.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um mecanismo de arbitragem que deve ser implementado para evitar possíveis colisões no barramento, quando mais de uma estação deseja transmitir uma mensagem.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha e dois fios simples, além de permitir a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Todos os protocolos de redes industriais são desenvolvidos para atuar apenas nos níveis de controle da automação, por isso utilizam o padrão elétrico de comunicação serial RS-232.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença III é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas a sentença I é falsa.

Apenas a sentença IV é falsa.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um símbolo na comunicação entre diversos dispositivos, onde somente o dispositivo mestre envia mensagens no barramento e os outros somente recebem as ordens.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha contendo um par de fio simples para comunicação e outro par de fio simples para alimentação em corrente contínua. A rede também permite a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Os protocolos de redes industriais são desenvolvidos para atuar nos níveis de controle da automação, por isso utilizam um padrão elétrico de comunicação de acordo com o local. É possível, em algumas redes, utiliza-la até mesmo em áreas classificadas junto com componentes que sejam aprovados e certificados por órgãos competentes.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença I é falsa.

Apenas a sentença II é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas as sentenças III e IV são verdadeiras.

O CLP que recebe dados de variáveis de processo e de pontos de ajuste em forma de sinal analógico expressará o erro como uma função analógica. Do mesmo modo, um sistema com um ponto de ajuste de 64 °C e uma variável de processo de 52 °C terá o erro em porcentagem de aproximadamente:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

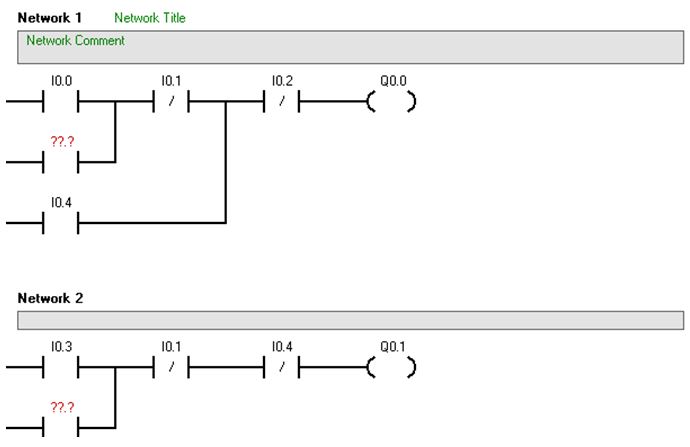

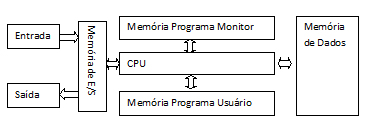

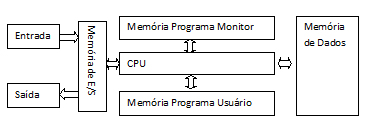

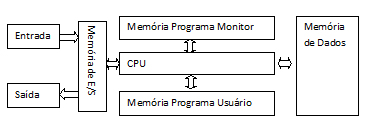

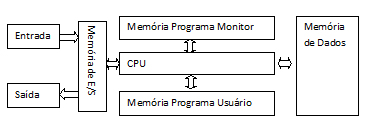

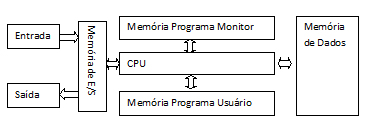

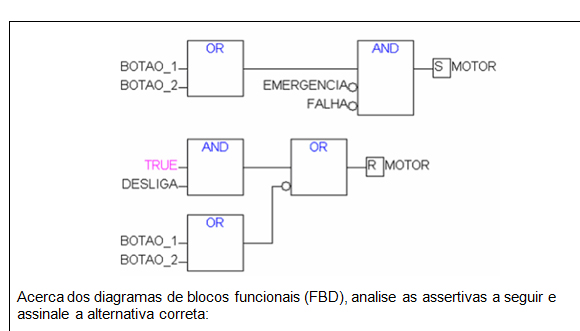

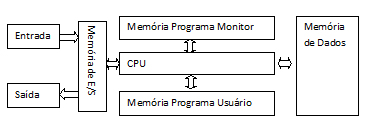

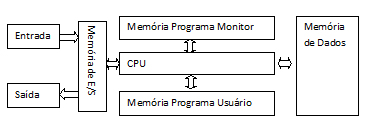

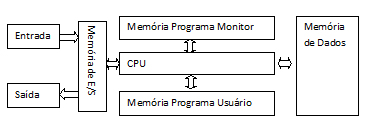

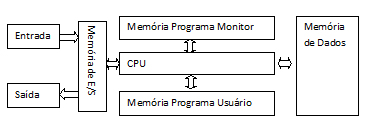

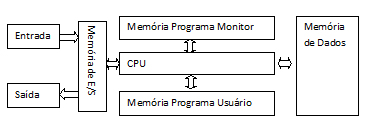

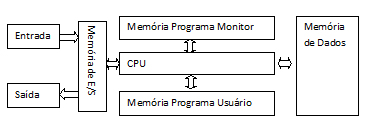

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

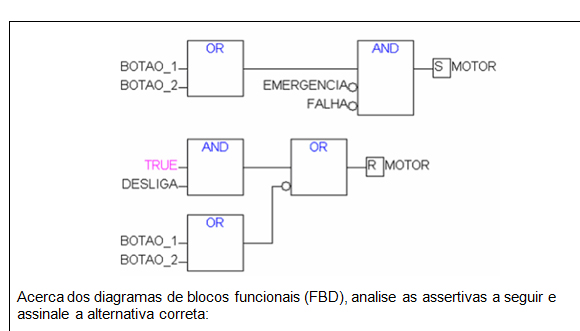

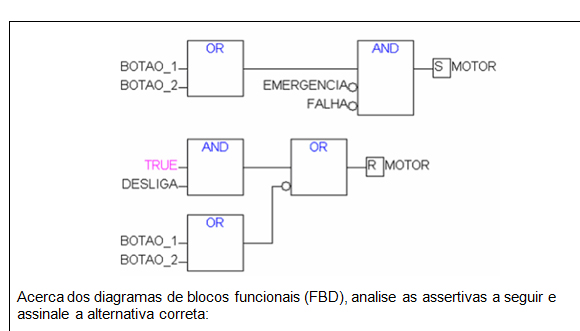

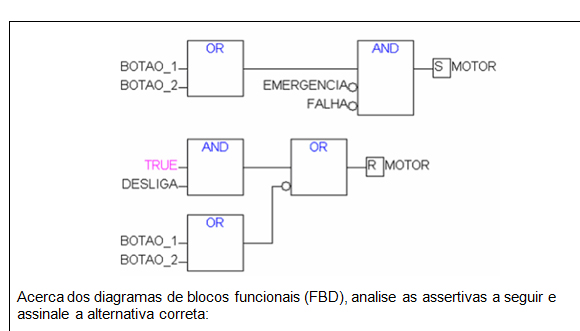

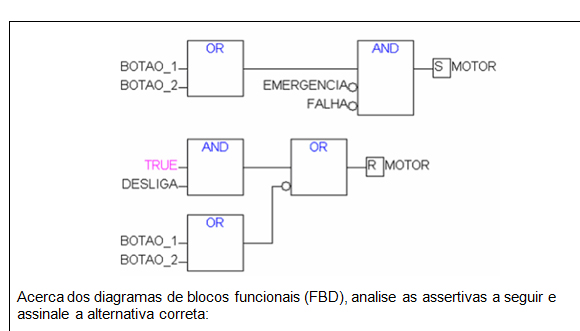

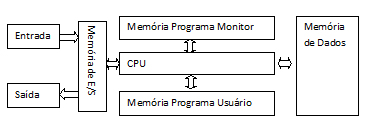

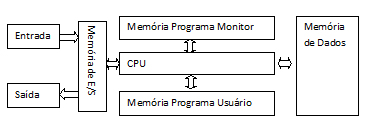

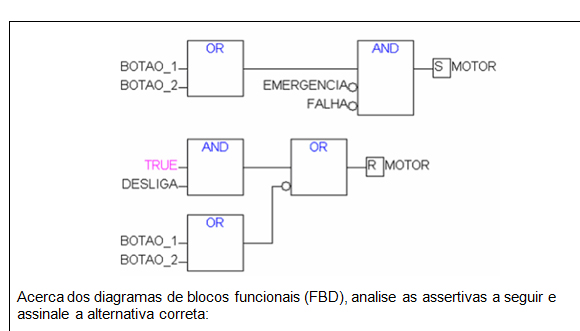

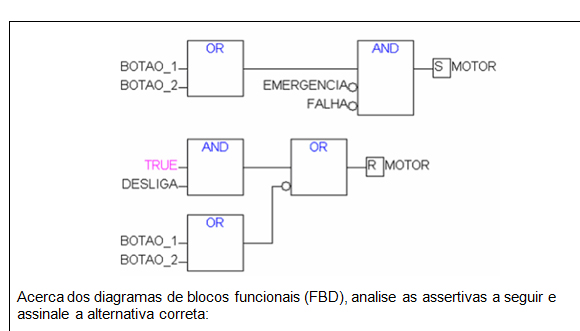

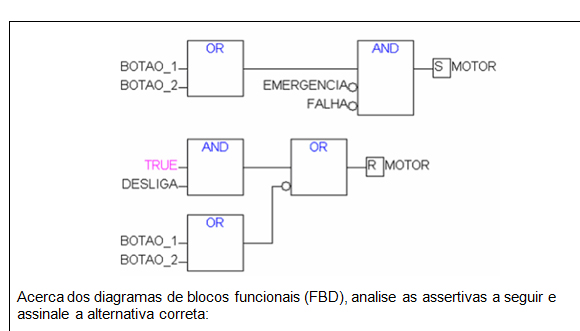

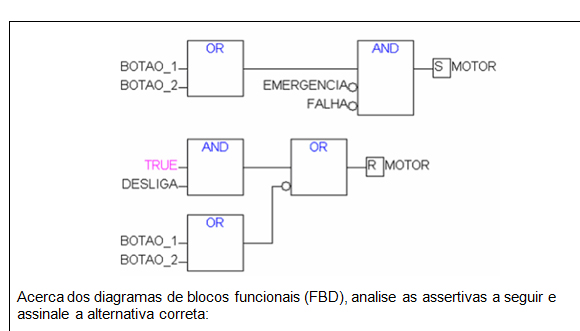

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Apenas as sentenças I e II são verdadeiras.

Todas as sentenças são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas a sentença IV é falsa.

Apenas a sentença I é falsa.

O circuito eletrônico usado é padrão para a maioria das malhas de controle, independente da variável sendo medida ou manipulada.

Acerca do controlador de ação direta, verifique as assertivas seguir:

I) Um controlador de ação direta é um controlador de malha fechada, cuja saída variável de controle aumenta em resposta a um aumento na variável de processo.

II) Um exemplo de aplicação de controlador de ação direta é um sistema de resfriamento de ar.

III) Um controlador de ação direta é um controlador de malha fechada, cuja saída variável de controle diminui em resposta a um aumento na variável de processo.

Está(ão) correta(s):

I e II.

Apenas a III.

II e III.

Apenas a II.

Apenas a I.

Verifique um programa do CLP para automatizar um carro transportador que deve funcionar da seguinte maneira: o operador pressiona um botão B1 para dar o comando, ligará o motor na direção preferencial do sensor S1. Uma vez o sensor de fim de curso S1 acionado, irá no movimento inverso, chegando em outro sensor fim de curso S2. A figura a seguir representa como deve ser o processo. Por fim, há um botão de parada B2.

Porém o programa está incompleto, bastando apenas nomear as funções:

Verifique as alternativas a seguir e veja qual completa corretamente o programa:

Network 1 → I0.0 e Network 2→ I0.1.

Network 1 → Q0.1 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.0.

Network 1 → I0.1 e Network 2→ I0.2.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um mecanismo de arbitragem que deve ser implementado para evitar possíveis colisões no barramento, quando mais de uma estação deseja transmitir uma mensagem.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha e dois fios simples, além de permitir a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Todos os protocolos de redes industriais são desenvolvidos para atuar apenas nos níveis de controle da automação, por isso utilizam o padrão elétrico de comunicação serial RS-232.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença III é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas a sentença I é falsa.

Apenas a sentença IV é falsa.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um símbolo na comunicação entre diversos dispositivos, onde somente o dispositivo mestre envia mensagens no barramento e os outros somente recebem as ordens.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha contendo um par de fio simples para comunicação e outro par de fio simples para alimentação em corrente contínua. A rede também permite a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Os protocolos de redes industriais são desenvolvidos para atuar nos níveis de controle da automação, por isso utilizam um padrão elétrico de comunicação de acordo com o local. É possível, em algumas redes, utiliza-la até mesmo em áreas classificadas junto com componentes que sejam aprovados e certificados por órgãos competentes.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença I é falsa.

Apenas a sentença II é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas as sentenças III e IV são verdadeiras.

O CLP que recebe dados de variáveis de processo e de pontos de ajuste em forma de sinal analógico expressará o erro como uma função analógica. Do mesmo modo, um sistema com um ponto de ajuste de 64 °C e uma variável de processo de 52 °C terá o erro em porcentagem de aproximadamente:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

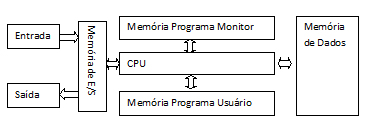

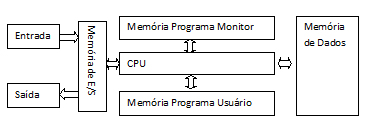

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

I e II.

Apenas a III.

II e III.

Apenas a II.

Apenas a I.

Verifique um programa do CLP para automatizar um carro transportador que deve funcionar da seguinte maneira: o operador pressiona um botão B1 para dar o comando, ligará o motor na direção preferencial do sensor S1. Uma vez o sensor de fim de curso S1 acionado, irá no movimento inverso, chegando em outro sensor fim de curso S2. A figura a seguir representa como deve ser o processo. Por fim, há um botão de parada B2.

Porém o programa está incompleto, bastando apenas nomear as funções:

Verifique as alternativas a seguir e veja qual completa corretamente o programa:

Network 1 → I0.0 e Network 2→ I0.1.

Network 1 → Q0.1 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.0.

Network 1 → I0.1 e Network 2→ I0.2.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um mecanismo de arbitragem que deve ser implementado para evitar possíveis colisões no barramento, quando mais de uma estação deseja transmitir uma mensagem.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha e dois fios simples, além de permitir a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Todos os protocolos de redes industriais são desenvolvidos para atuar apenas nos níveis de controle da automação, por isso utilizam o padrão elétrico de comunicação serial RS-232.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença III é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas a sentença I é falsa.

Apenas a sentença IV é falsa.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um símbolo na comunicação entre diversos dispositivos, onde somente o dispositivo mestre envia mensagens no barramento e os outros somente recebem as ordens.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha contendo um par de fio simples para comunicação e outro par de fio simples para alimentação em corrente contínua. A rede também permite a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Os protocolos de redes industriais são desenvolvidos para atuar nos níveis de controle da automação, por isso utilizam um padrão elétrico de comunicação de acordo com o local. É possível, em algumas redes, utiliza-la até mesmo em áreas classificadas junto com componentes que sejam aprovados e certificados por órgãos competentes.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença I é falsa.

Apenas a sentença II é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas as sentenças III e IV são verdadeiras.

O CLP que recebe dados de variáveis de processo e de pontos de ajuste em forma de sinal analógico expressará o erro como uma função analógica. Do mesmo modo, um sistema com um ponto de ajuste de 64 °C e uma variável de processo de 52 °C terá o erro em porcentagem de aproximadamente:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Network 1 → I0.0 e Network 2→ I0.1.

Network 1 → Q0.1 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.1.

Network 1 → Q0.0 e Network 2→ Q0.0.

Network 1 → I0.1 e Network 2→ I0.2.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um mecanismo de arbitragem que deve ser implementado para evitar possíveis colisões no barramento, quando mais de uma estação deseja transmitir uma mensagem.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha e dois fios simples, além de permitir a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Todos os protocolos de redes industriais são desenvolvidos para atuar apenas nos níveis de controle da automação, por isso utilizam o padrão elétrico de comunicação serial RS-232.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença III é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas a sentença I é falsa.

Apenas a sentença IV é falsa.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um símbolo na comunicação entre diversos dispositivos, onde somente o dispositivo mestre envia mensagens no barramento e os outros somente recebem as ordens.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha contendo um par de fio simples para comunicação e outro par de fio simples para alimentação em corrente contínua. A rede também permite a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Os protocolos de redes industriais são desenvolvidos para atuar nos níveis de controle da automação, por isso utilizam um padrão elétrico de comunicação de acordo com o local. É possível, em algumas redes, utiliza-la até mesmo em áreas classificadas junto com componentes que sejam aprovados e certificados por órgãos competentes.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença I é falsa.

Apenas a sentença II é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas as sentenças III e IV são verdadeiras.

O CLP que recebe dados de variáveis de processo e de pontos de ajuste em forma de sinal analógico expressará o erro como uma função analógica. Do mesmo modo, um sistema com um ponto de ajuste de 64 °C e uma variável de processo de 52 °C terá o erro em porcentagem de aproximadamente:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Apenas a sentença II é verdadeira.

Apenas a sentença III é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas a sentença I é falsa.

Apenas a sentença IV é falsa.

A respeito das redes industriais e de suas tecnologias e protocolos, analise as assertivas a seguir:

I - O barramento, também chamado de token, é um símbolo na comunicação entre diversos dispositivos, onde somente o dispositivo mestre envia mensagens no barramento e os outros somente recebem as ordens.

II - Com o sistema PROFIBUS PA, a medição e o controle podem ser transmitidos por uma linha contendo um par de fio simples para comunicação e outro par de fio simples para alimentação em corrente contínua. A rede também permite a manutenção e a conexão/desconexão de equipamentos até mesmo durante a operação sem interferir em outras estações.

III - O protocolo de comunicação da PROFIBUS PA é o mesmo do PROFIBUS DP.

IV - Os protocolos de redes industriais são desenvolvidos para atuar nos níveis de controle da automação, por isso utilizam um padrão elétrico de comunicação de acordo com o local. É possível, em algumas redes, utiliza-la até mesmo em áreas classificadas junto com componentes que sejam aprovados e certificados por órgãos competentes.

É CORRETO apenas o que se afirma em:

Apenas a sentença II é verdadeira.

Apenas a sentença I é falsa.

Apenas a sentença II é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas as sentenças III e IV são verdadeiras.

O CLP que recebe dados de variáveis de processo e de pontos de ajuste em forma de sinal analógico expressará o erro como uma função analógica. Do mesmo modo, um sistema com um ponto de ajuste de 64 °C e uma variável de processo de 52 °C terá o erro em porcentagem de aproximadamente:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Apenas a sentença II é verdadeira.

Apenas a sentença I é falsa.

Apenas a sentença II é falsa.

Apenas as sentenças II e III são verdadeiras.

Apenas as sentenças III e IV são verdadeiras.

O CLP que recebe dados de variáveis de processo e de pontos de ajuste em forma de sinal analógico expressará o erro como uma função analógica. Do mesmo modo, um sistema com um ponto de ajuste de 64 °C e uma variável de processo de 52 °C terá o erro em porcentagem de aproximadamente:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

18.75 %

-11.25 %

13.88 %

81.25 %

-9.75 %

Dado o texto a seguir:

“é uma medida que expressa o grau de dispersão de um conjunto de dados.” (TODAMATERIA, 2021)

Representa qual método de interpretação de dados?

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Mediana

Desvio padrão

Moda

Média

Desvio padrão médio

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função de um sistema operacional do CLP, que possui as funções de sistema como diagnóstico e inicialização.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Apenas a sentença IV é falsa.

Apenas a sentença I é verdadeira.

Apenas as sentenças I e III são verdadeiras.

Apenas a sentença II é verdadeira.

Apenas as sentenças II e IV são verdadeiras.

A Unidade Central de Processamento (UCP) é mais conhecida pela sigla CPU, que, em inglês, significa Central Processing Unit. É a CPU que executa a lógica de controle, mas, para isso, usa a memória, como podemos ver na figura a seguir.

Verifique as assertivas a seguir:

I - Memória do Programa Monitor: o programa monitor é aquele que tem a função alimentar os dados disponibilizados para supervisão da operação, como os sistemas supervisórios.

II - Memória do Programa do Usuário: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

III - Memória de dados: é a região de memória destinada a armazenar temporariamente os dados gerados pelo programa do usuário, tais como: valores de temporizadores, valores de contadores, códigos de erro, senhas de acesso.

IV - O sistema operacional é gravado pelo fabricante, geralmente armazenado em memórias como as RAM ou SRAM.

Marquie a alterantiva CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.

Os diagramas de blocos funcionais (FBD) é uma linguagem gráfica que descreve a função entre variáveis de entrada e variáveis de saída. Uma função é descrita como um conjunto de blocos elementares. As variáveis de entrada e de saída são conectadas a blocos por linhas de conexão, chamadas também de links, essas linhas conectam dois pontos lógicos do diagrama; a conexão é orientada, ou seja, significa que carrega dados. Na figura, um exemplo de aplicação do FBD:

I - As aplicações de Blocos Funcionais são apenas para modelagem, funcionando como um fluxograma, documentando a lógica a ser seguida e implementada em outra linguagem.

II - O modelo de bloco funcional é um algoritmo de tempo real, que transforma parâmetros de entrada em parâmetros de saída.

III - Todos os CLPs, independente da categoria e do fabricante, conseguem trabalhar com a linguagem de bloco funcional, visto que essa linguagem é padronizada pela IEC 61131-3.

IV - Para suportar o acesso à interface de informação de operação durante a execução de bloco funcional, dois níveis de rede de acesso são definidos: um de tráfego operacional e um de tráfego de segundo plano.

Assinale a alternativa CORRETA:

Apenas a sentença I é falsa.

Apenas a sentença III é verdadeira.

Apenas a sentença I é verdadeira.

Apenas a sentença II é falsa.

Apenas a sentença IV é verdadeira.